Learning Verilog for FPGA Development

.MP4, AVC, 1280x720, 30 fps | English, AAC, 2 Ch | 2h 2m | 251 MB

Instructor: Eduardo Corpeño

.MP4, AVC, 1280x720, 30 fps | English, AAC, 2 Ch | 2h 2m | 251 MB

Instructor: Eduardo Corpeño

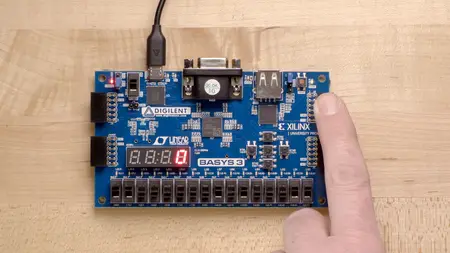

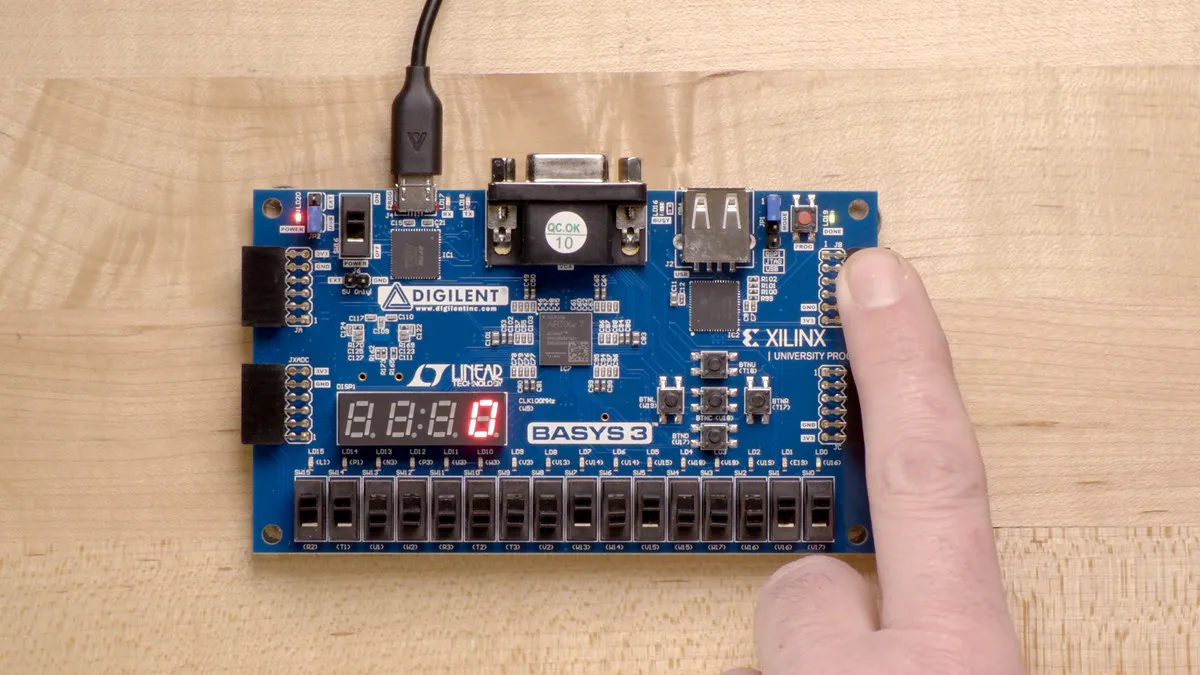

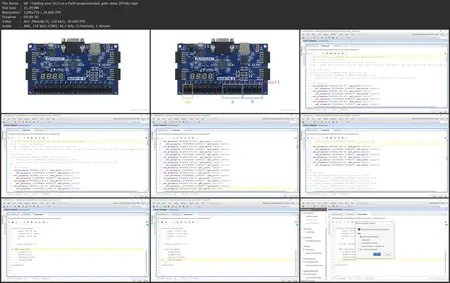

FPGA development requires a big switch from more typical programming processes. In order to get an FPGA-based embedded system up and running, developers must add a hardware description language to their repertoire. In this course, Eduardo Corpeño helps you learn the fundamentals of one such language: the popular and concise Verilog.

Eduardo begins with the basics; he explains what a hardware description language is and some similarities to traditional programming languages. He then covers the basic syntax of Verilog, as well as how to create test bench modules to run simulations, use variables with operators as an advantage of the behavioral level of abstraction, and more. Along the way, he provides demos and programming challenges that allow you to put your new skills to the test.

Learning objectives

- The purpose of hardware description languages

- The different abstraction levels of a digital system

- The structure and syntax of a module in Verilog

- The uses of range specification

- If-else statements

- Boolean expressions

- The nature and limitations of simulations

- Combinational and sequential systems